低功耗集成電路設計中的寄存器傳輸功耗優化策略

在現代集成電路設計中,功耗已成為與性能、面積同等重要的關鍵設計指標。隨著工藝節點不斷縮小,動態功耗與漏電功耗的挑戰日益嚴峻,其中寄存器傳輸級(Register Transfer Level, RTL)的功耗優化是低功耗設計的重要環節。寄存器傳輸操作頻繁,其功耗貢獻顯著,因此,系統性地解決寄存器傳輸功耗問題對于實現高效能、低功耗的芯片至關重要。

一、寄存器傳輸功耗的主要來源

寄存器傳輸功耗主要源于兩個核心部分:

- 組合邏輯切換功耗:數據在寄存器之間通過組合邏輯電路傳輸時,邏輯門的開關活動會產生動態功耗。這是寄存器傳輸中主要的動態功耗來源。

- 寄存器本身的操作功耗:包括時鐘網絡對寄存器時鐘端的充電/放電功耗(時鐘功耗),以及寄存器數據采樣、保持所消耗的功耗。時鐘功耗通常是芯片動態功耗的很大一部分。

二、解決寄存器傳輸功耗的關鍵技術

針對上述來源,在RTL設計和綜合階段可以采用多層次、多粒度的優化策略。

1. 時鐘門控技術

這是降低寄存器相關功耗最有效且廣泛應用的技術。其核心思想是:當寄存器組不需要更新數據時,關閉其時鐘信號,從而消除不必要的時鐘翻轉帶來的功耗。

- 基于RTL的時鐘門控:設計時顯式地為功能模塊或寄存器塊添加使能信號,綜合工具可將其自動推斷為集成時鐘門控單元。

- 自動時鐘門控:現代綜合工具可以在門級網表中自動識別寄存器的使能條件,并插入時鐘門控單元。合理使用時鐘門控可大幅降低時鐘網絡的動態功耗。

2. 操作數隔離

當組合邏輯電路的輸入變化不會影響其輸出時,該邏輯的開關活動就是多余的。操作數隔離技術通過在邏輯電路的輸入端插入門控電路,在輸出無需變化時“凍結”輸入,阻止信號變化向后續邏輯傳播,從而減少不必要的開關活動。這在數據通路、多路選擇器等結構中效果顯著。

3. 數據編碼與總線反演

通過改變數據的表示形式來減少總線上的信號跳變次數。例如,總線反演技術會在傳輸數據前,判斷是否將數據取反后傳輸能使跳變位數更少,并增加一位標志位來指示是否進行了取反。接收端根據標志位恢復原始數據。這對于高負載、長距離的總線傳輸尤其有效。

4. 存儲器與寄存器文件分區訪問

大型的寄存器文件或存儲器模塊每次訪問都會激活整個陣列,功耗巨大。將其劃分為多個較小的、可獨立使能的區塊,每次只訪問所需數據所在的區塊,可以顯著降低激活功耗。這需要在架構設計時就進行規劃。

5. 流水線級優化與邏輯重組

通過調整流水線結構、平衡各級延遲,可以降低工作電壓或頻率,從而平方級地降低動態功耗。對關鍵路徑上的邏輯進行重組和優化,減少邏輯深度和毛刺產生,也能有效降低組合邏輯的切換活動率。

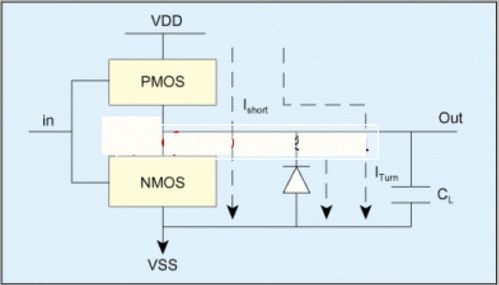

6. 多電壓域與電源門控

在系統級,可以為不同性能要求的模塊分配不同的工作電壓。對于長時間閑置的功能模塊,可以完全切斷其電源(電源門控),將漏電功耗降至近乎為零。這需要精細的電源管理架構和電平轉換、隔離單元的支持。

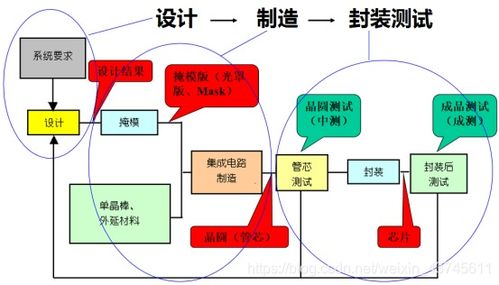

三、設計流程與工具協同

有效的低功耗設計依賴于從架構到物理實現的全程把控:

- 早期評估:在架構和RTL設計階段,使用功耗預估工具分析不同設計選擇的功耗影響。

- RTL設計與綜合:采用可綜合的低功耗設計描述(如正確使用時鐘門控使能信號),并設定綜合工具的低功耗優化約束與策略。

- 驗證:進行功能驗證的也需要進行功耗意圖的統一格式(如UPF/CPF)驗證,確保低功耗設計在實現中不會引入功能錯誤。

- 物理實現與簽核:在布局布線階段實施時鐘樹綜合優化、電源網絡規劃,并在簽核階段進行包含各種工作模式的精確功耗分析。

解決寄存器傳輸功耗問題是一個系統工程,需要將多種技術有機結合,并在設計流程的各個階段予以貫徹。從最前端的架構決策,到RTL編碼風格,再到后端實現策略,每一個環節都對最終芯片的功耗表現有著深遠影響。隨著人工智能、物聯網等應用對能效比要求的極致化,掌握并靈活運用這些低功耗設計技術,已成為當代集成電路設計師的核心能力之一。

如若轉載,請注明出處:http://www.vzhmvet.cn/product/93.html

更新時間:2026-04-10 10:26:53